D-FET 0 गेट बायसमध्ये आहे जेव्हा चॅनेलचे अस्तित्व, FET आयोजित करू शकते; ई-एफईटी 0 गेट बायसमध्ये आहे जेव्हा कोणतेही चॅनल नसते, FET आयोजित करू शकत नाही. या दोन प्रकारच्या FET ची स्वतःची वैशिष्ट्ये आणि उपयोग आहेत. सर्वसाधारणपणे, हाय-स्पीड, लो-पॉवर सर्किट्समध्ये वर्धित FET खूप मौल्यवान आहे; आणि हे उपकरण कार्यरत आहे, हे गेट बायस vo ची ध्रुवीयता आहेltage आणि निचरा समान व्होल्टेज, सर्किट डिझाइनमध्ये ते अधिक सोयीस्कर आहे.

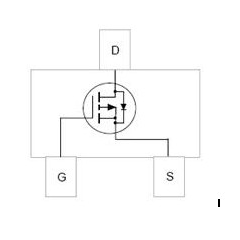

तथाकथित वर्धित म्हणजे: जेव्हा व्हीजीएस = 0 ट्यूब कट-ऑफ स्थिती असते, तसेच योग्य व्हीजीएस असते, तेव्हा बहुतेक वाहक गेटकडे आकर्षित होतात, अशा प्रकारे या प्रदेशातील वाहक "वर्धित" करतात, एक प्रवाहकीय चॅनेल तयार करतात. n-चॅनेल वर्धित MOSFET हे मुळात डावे-उजवे सममितीय टोपोलॉजी आहे, जे SiO2 फिल्म इन्सुलेशनच्या लेयरच्या निर्मितीवर P-प्रकार सेमीकंडक्टर आहे. हे पी-टाइप सेमीकंडक्टरवर SiO2 फिल्मचा इन्सुलेटिंग लेयर तयार करते आणि नंतर दोन उच्च डोप केलेल्या एन-टाइप क्षेत्रांमध्ये पसरते.फोटोलिथोग्राफी, आणि N-प्रकारच्या प्रदेशातून लीड्स इलेक्ट्रोड्स, एक ड्रेन D साठी आणि एक स्त्रोत S साठी. ॲल्युमिनियम धातूचा एक थर स्त्रोत आणि ड्रेन दरम्यानच्या इन्सुलेटिंग लेयरवर गेट G म्हणून प्लेट केला जातो. जेव्हा VGS = 0 V , ड्रेन आणि स्त्रोत यांच्यामध्ये बॅक-टू- बॅक डायोड असलेले बरेच डायोड आहेत आणि D आणि S मधील व्होल्टेज D आणि दरम्यान विद्युत प्रवाह तयार करत नाही. S. D आणि S मधील विद्युतप्रवाह लागू केलेल्या व्होल्टेजने तयार होत नाही.

जेव्हा गेट व्होल्टेज जोडला जातो, जर 0 < VGS < VGS(th), गेट आणि सब्सट्रेट दरम्यान तयार झालेल्या कॅपेसिटिव्ह इलेक्ट्रिक फील्डद्वारे, गेटच्या तळाशी असलेल्या पी-टाइप सेमीकंडक्टरमधील पॉलीऑन होल खाली वळवले जातात आणि नकारात्मक आयनांचा पातळ क्षीण थर दिसून येतो; त्याच वेळी, ते पृष्ठभागाच्या स्तरावर जाण्यासाठी त्यातील ऑलिगॉन्सना आकर्षित करेल, परंतु ड्रेन आणि स्त्रोताशी संवाद साधणारी प्रवाहकीय वाहिनी तयार करण्यासाठी संख्या मर्यादित आणि अपुरी आहे, म्हणून ड्रेन करंट आयडी तयार करण्यासाठी ते अद्याप अपुरे आहे. आणखी वाढ VGS, जेव्हा VGS > VGS (th) (VGS (th) ला टर्न-ऑन व्होल्टेज म्हणतात), कारण यावेळी गेट व्होल्टेज तुलनेने मजबूत आहे, P-प्रकारातील सेमीकंडक्टर पृष्ठभागाच्या थरात गेटच्या तळाशी अधिक गोळा होतात. इलेक्ट्रॉन, आपण एक खंदक, नाला आणि संप्रेषणाचे स्त्रोत बनवू शकता. यावेळी ड्रेन स्त्रोत व्होल्टेज जोडल्यास, ड्रेन करंट आयडी बनू शकतो. प्रवाहकीय वाहिनीमधील इलेक्ट्रॉन्स गेटच्या खाली तयार होतात, कारण P-प्रकार सेमीकंडक्टर ध्रुवीय वाहक छिद्र विरुद्ध आहे, म्हणून त्याला अँटी-टाइप लेयर म्हणतात. VGS जसजसा वाढत जाईल, तसतसा ID वाढत जाईल. VGS = 0V वर ID = 0, आणि ड्रेन करंट VGS > VGS(th) नंतरच होतो, म्हणून, या प्रकारच्या MOSFET ला एन्हांसमेंट MOSFET म्हणतात.

ड्रेन करंटवरील व्हीजीएसच्या नियंत्रण संबंधाचे वर्णन वक्र iD = f(VGS(th))|VDS=const, ज्याला हस्तांतरण वैशिष्ट्यपूर्ण वक्र म्हणतात, आणि हस्तांतरण वैशिष्ट्यपूर्ण वक्र, gm, च्या उताराची विशालता द्वारे केले जाऊ शकते. गेट स्रोत व्होल्टेजद्वारे ड्रेन करंटचे नियंत्रण प्रतिबिंबित करते. gm चे परिमाण mA/V आहे, म्हणून gm ला transconductance असेही म्हणतात.