MOSFETs ची भूमिका काय आहे?

MOSFETs संपूर्ण वीज पुरवठा प्रणालीच्या व्होल्टेजचे नियमन करण्यात भूमिका बजावतात. सध्या, बोर्डवर अनेक MOSFETs वापरले जात नाहीत, साधारणतः 10. मुख्य कारण म्हणजे बहुतेक MOSFETs IC चिपमध्ये एकत्रित केले जातात. MOSFET ची मुख्य भूमिका ॲक्सेसरीजसाठी स्थिर व्होल्टेज प्रदान करणे आहे, म्हणून ते सामान्यतः CPU, GPU आणि सॉकेट इत्यादींमध्ये वापरले जाते.MOSFETsसाधारणपणे वर आणि खाली दोन गटाच्या स्वरूपात बोर्डवर दिसतात.

MOSFET पॅकेज

उत्पादनातील MOSFET चिप पूर्ण झाली आहे, आपल्याला MOSFET चिपमध्ये एक शेल जोडण्याची आवश्यकता आहे, म्हणजेच MOSFET पॅकेज. MOSFET चिप शेलमध्ये सपोर्ट, प्रोटेक्शन, कूलिंग इफेक्ट आहे, परंतु चिपला इलेक्ट्रिकल कनेक्शन आणि अलगाव प्रदान करण्यासाठी देखील आहे, जेणेकरुन MOSFET डिव्हाइस आणि इतर घटक संपूर्ण सर्किट तयार करू शकतील.

पीसीबी मध्ये स्थापनेनुसार फरक ओळखण्यासाठी,MOSFETपॅकेजमध्ये दोन मुख्य श्रेणी आहेत: होल आणि सरफेस माउंटद्वारे. PCB वर वेल्डेड PCB माउंटिंग होलद्वारे MOSFET पिन घातली आहे. सरफेस माउंट हे MOSFET पिन आणि हीट सिंक फ्लँज आहे जे PCB पृष्ठभाग पॅडवर वेल्डेड केले जाते.

पॅकेजसाठी मानक पॅकेज तपशील

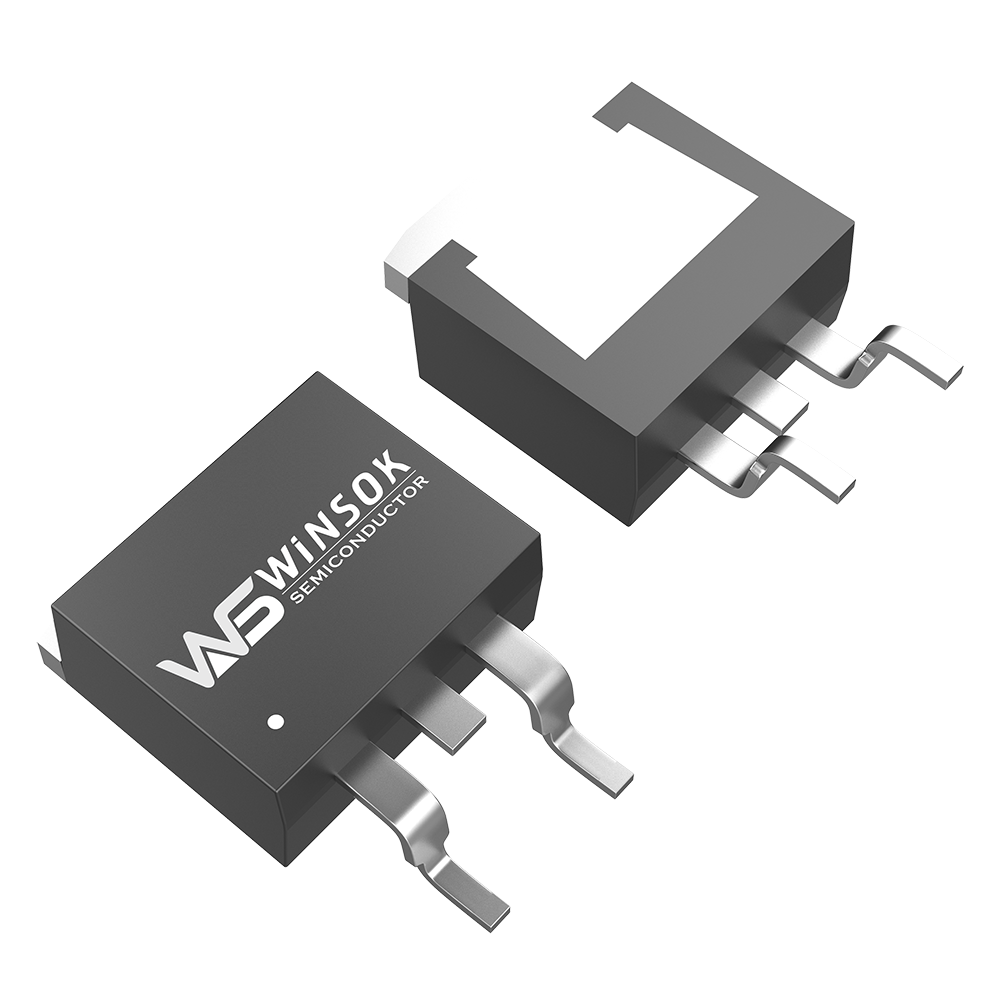

TO (ट्रांझिस्टर आउट-लाइन) हे सुरुवातीचे पॅकेज तपशील आहे, जसे की TO-92, TO-92L, TO-220, TO-252, इत्यादी प्लग-इन पॅकेज डिझाइन आहेत. अलिकडच्या वर्षांत, पृष्ठभाग माउंट मार्केटची मागणी वाढली आहे, आणि TO पॅकेजेसने सरफेस माउंट पॅकेजेसची प्रगती केली आहे.

TO-252 आणि TO263 हे पृष्ठभाग माउंट पॅकेजेस आहेत. TO-252 ला D-PAK आणि TO-263 ला D2PAK म्हणून देखील ओळखले जाते.

D-PAK पॅकेज MOSFET मध्ये तीन इलेक्ट्रोड आहेत, गेट (G), ड्रेन (D), स्रोत (S). ड्रेन (डी) पैकी एक पिन ड्रेन (डी) साठी हीट सिंकच्या मागील बाजूस न वापरता कापला जातो, थेट पीसीबीला वेल्डेड केला जातो, एकीकडे, उच्च प्रवाहाच्या आउटपुटसाठी, एकीकडे, पीसीबी उष्णता नष्ट होणे. तर तीन पीसीबी डी-पीएके पॅड आहेत, ड्रेन (डी) पॅड मोठा आहे.

पॅकेज TO-252 पिन डायग्राम

चिप पॅकेज लोकप्रिय किंवा ड्युअल इन-लाइन पॅकेज, ज्याला DIP (ड्युअल ln-लाइन पॅकेज) म्हणून संदर्भित केले जाते. त्या वेळी डीआयपी पॅकेजमध्ये योग्य पीसीबी (प्रिंटेड सर्किट बोर्ड) छिद्रित स्थापना असते, TO-प्रकार पॅकेज पीसीबी वायरिंग आणि ऑपरेशनपेक्षा सोपे असते. अधिक सोयीस्कर आहे आणि त्याचप्रमाणे त्याच्या पॅकेजच्या संरचनेची काही वैशिष्ट्ये मल्टी-लेयर सिरेमिक ड्युअल इन-लाइन डीआयपीसह अनेक फॉर्मच्या स्वरूपात आहेत. सिंगल-लेयर सिरेमिक ड्युअल इन-लाइन

डीआयपी, लीड फ्रेम डीआयपी आणि असेच. सामान्यतः पॉवर ट्रान्झिस्टर, व्होल्टेज रेग्युलेटर चिप पॅकेजमध्ये वापरले जाते.

चिपMOSFETपॅकेज

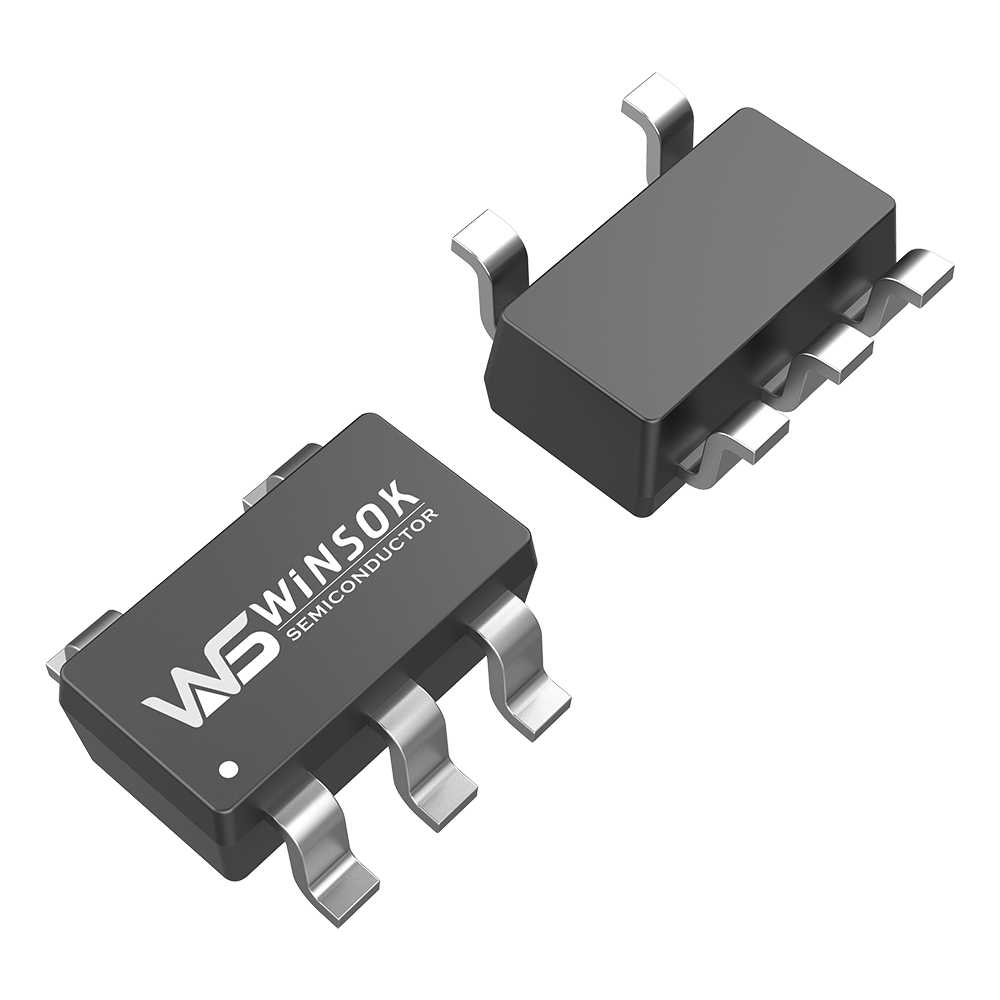

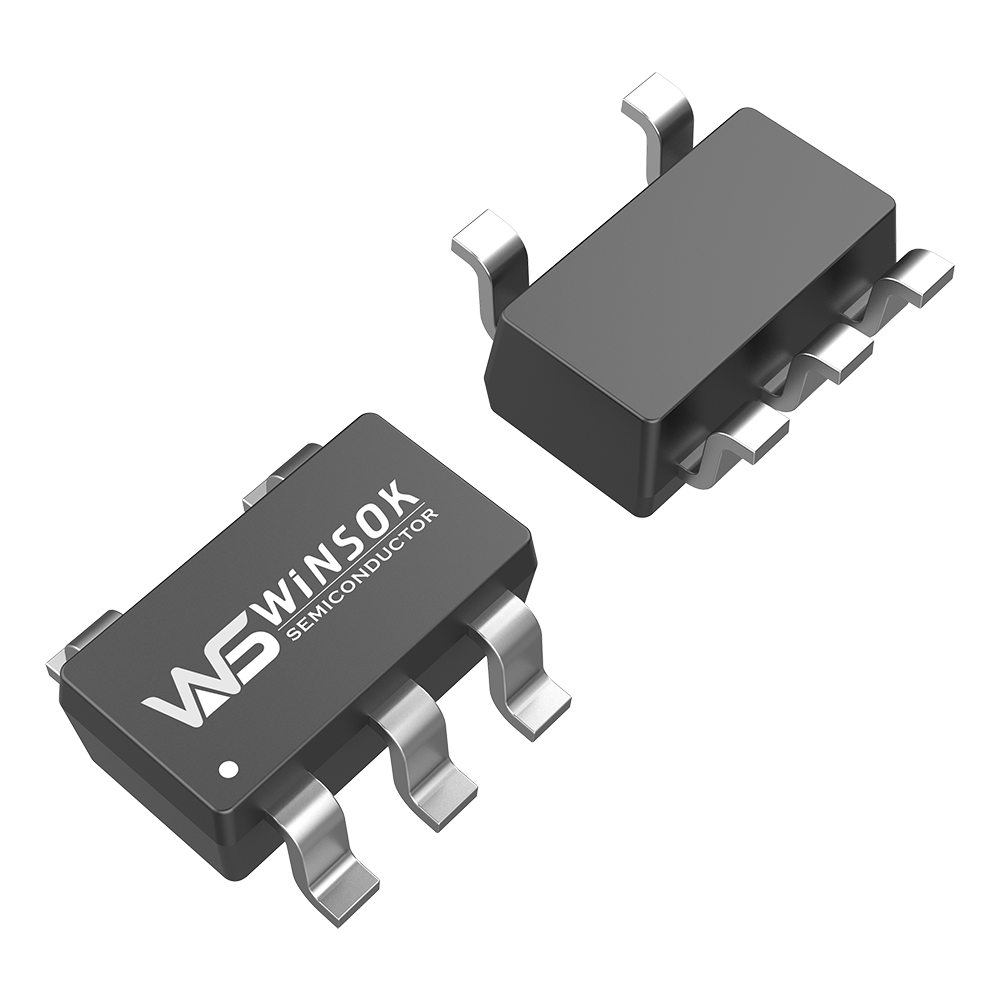

SOT पॅकेज

SOT (स्मॉल आउट-लाइन ट्रान्झिस्टर) एक लहान बाह्यरेखा ट्रान्झिस्टर पॅकेज आहे. हे पॅकेज एक SMD लहान पॉवर ट्रान्झिस्टर पॅकेज आहे, TO पॅकेजपेक्षा लहान, सामान्यतः लहान पॉवर MOSFET साठी वापरले जाते.

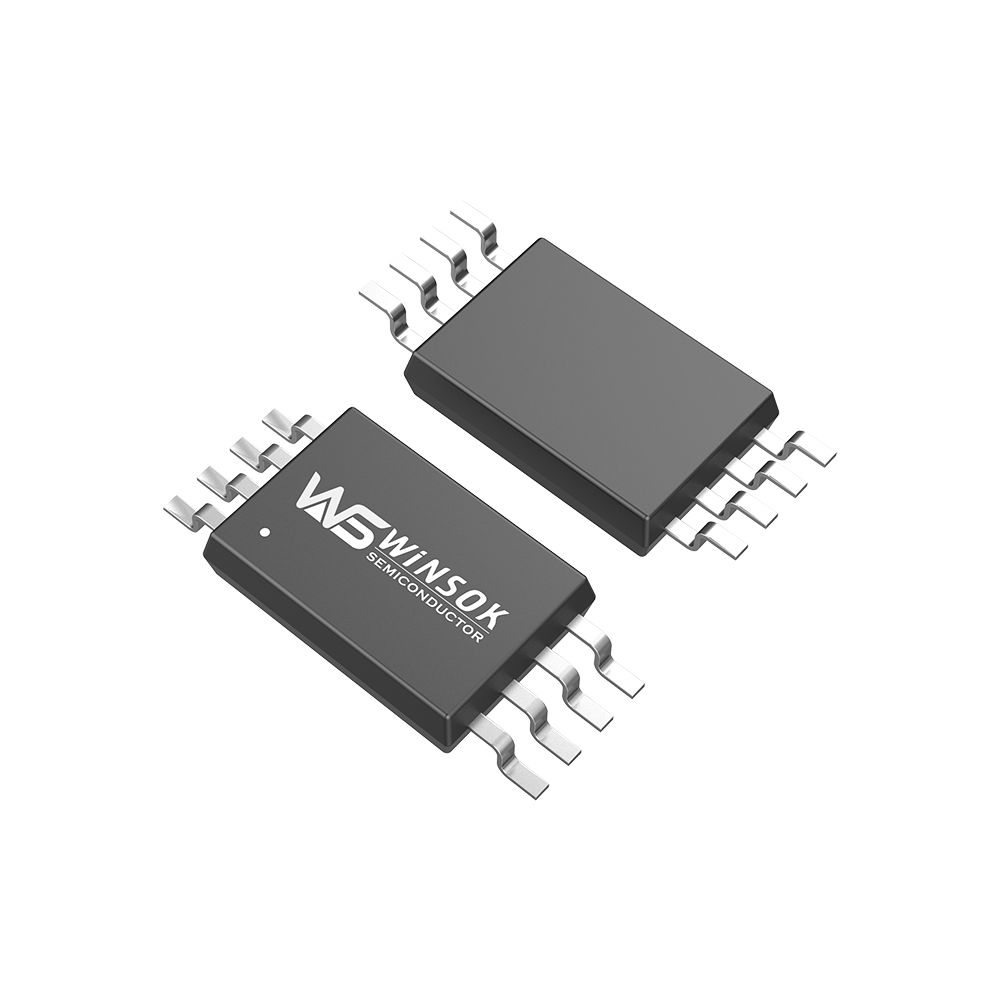

SOP पॅकेज

SOP (स्मॉल आउट-लाइन पॅकेज) चा अर्थ चीनी भाषेत "स्मॉल आउटलाइन पॅकेज" आहे, SOP हे पृष्ठभागाच्या माउंट पॅकेजपैकी एक आहे, पॅकेजच्या दोन्ही बाजूंच्या पिन गुलच्या पंखाच्या आकारात (एल-आकार), सामग्री प्लास्टिक आणि सिरेमिक आहे. SOP ला SOL आणि DFP देखील म्हणतात. SOP पॅकेज मानकांमध्ये SOP-8, SOP-16, SOP-20, SOP-28 इत्यादींचा समावेश होतो. SOP नंतरची संख्या पिनची संख्या दर्शवते.

MOSFET चे SOP पॅकेज बहुतेक SOP-8 स्पेसिफिकेशनचा अवलंब करते, उद्योग SO (स्मॉल आउट-लाइन) नावाचे "P" वगळण्याचा प्रयत्न करतात.

SMD MOSFET पॅकेज

SO-8 प्लॅस्टिक पॅकेज, थर्मल बेस प्लेट नाही, खराब उष्णता नष्ट होणे, सामान्यतः कमी-शक्ती MOSFET साठी वापरले जाते.

SO-8 प्रथम PHILIP द्वारे विकसित केले गेले होते, आणि नंतर हळूहळू TSOP (पातळ लहान बाह्यरेखा पॅकेज), VSOP (अतिशय लहान बाह्यरेखा पॅकेज), SSOP (कमी केलेले SOP), TSSOP (पातळ कमी केलेले SOP) आणि इतर मानक वैशिष्ट्यांमधून घेतले गेले.

या व्युत्पन्न पॅकेज वैशिष्ट्यांपैकी, TSOP आणि TSSOP सामान्यतः MOSFET पॅकेजेससाठी वापरले जातात.

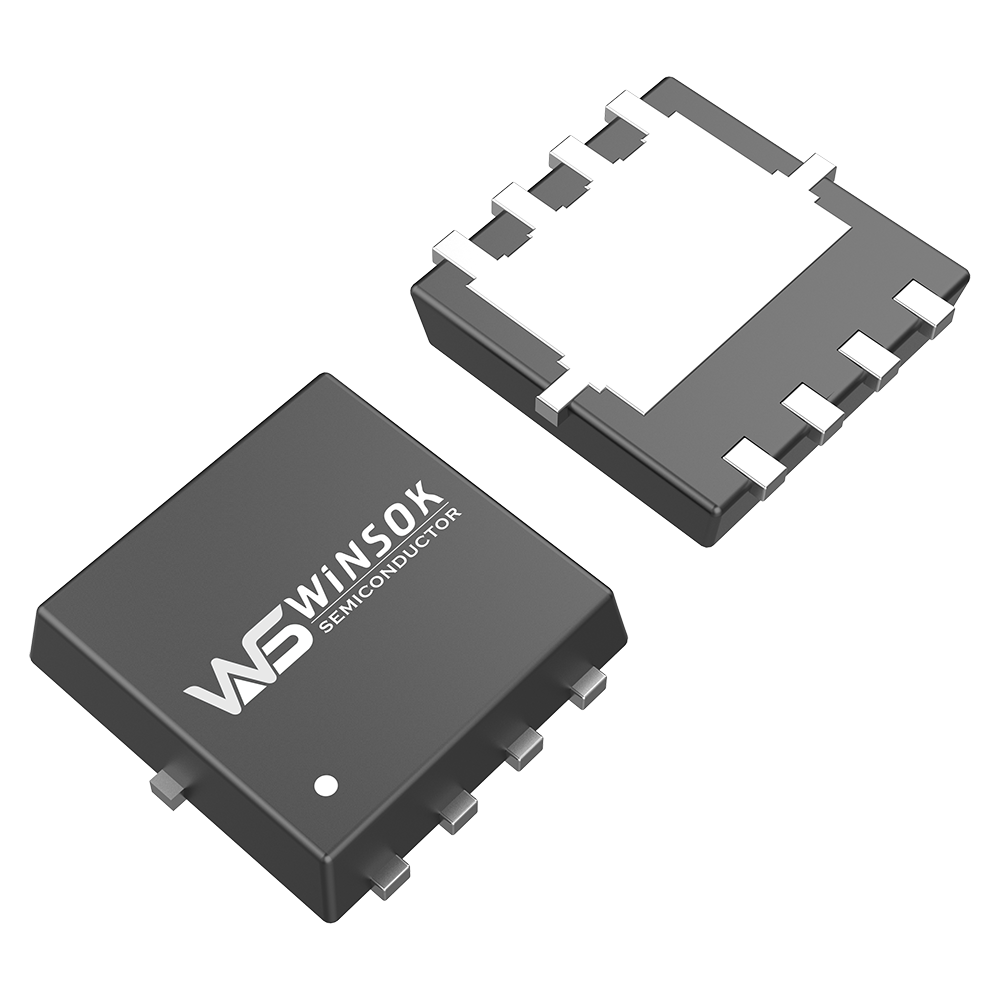

चिप MOSFET पॅकेजेस

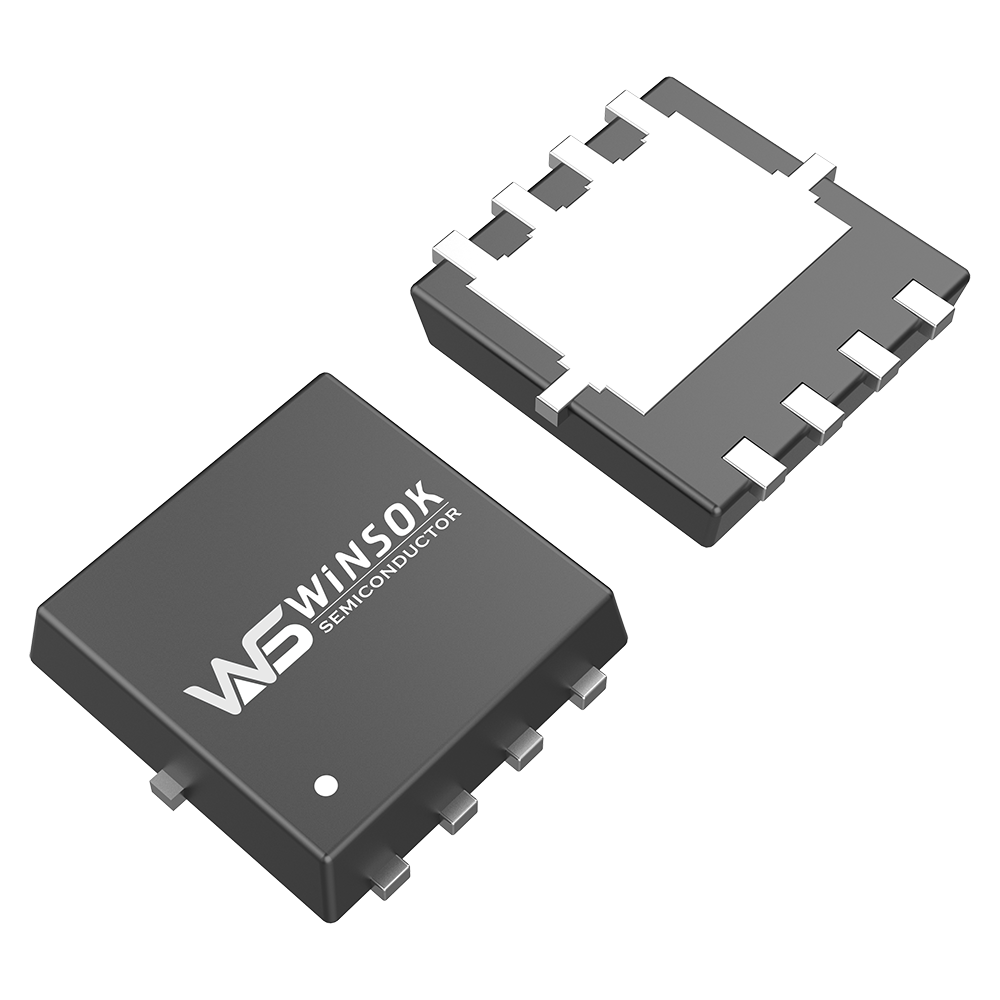

क्यूएफएन (क्वाड फ्लॅट नॉन-लीडेड पॅकेज) हे पृष्ठभागाच्या माउंट पॅकेजपैकी एक आहे, चिनी भाषेला फोर-साइड नॉन-लीडेड फ्लॅट पॅकेज म्हणतात, पॅडचा आकार लहान, लहान, प्लॅस्टिकचा आहे कारण उदयोन्मुख पृष्ठभाग माउंट चिपची सीलिंग सामग्री आहे. पॅकेजिंग तंत्रज्ञान, आता अधिक सामान्यतः LCC म्हणून ओळखले जाते. याला आता LCC म्हणतात, आणि QFN हे जपान इलेक्ट्रिकल आणि मेकॅनिकल इंडस्ट्रीज असोसिएशनने निश्चित केलेले नाव आहे. पॅकेज सर्व बाजूंनी इलेक्ट्रोड संपर्कांसह कॉन्फिगर केले आहे.

पॅकेज चारही बाजूंनी इलेक्ट्रोड संपर्कांसह कॉन्फिगर केलेले आहे आणि तेथे कोणतेही लीड नसल्यामुळे, माउंटिंग क्षेत्र QFP पेक्षा लहान आहे आणि उंची QFP पेक्षा कमी आहे. हे पॅकेज एलसीसी, पीसीएलसी, पी-एलसीसी, इ. म्हणूनही ओळखले जाते.